Steuerplatine für die Zentrale

Dieses Teilprojekt gehört zum Hochspannungs-Impulsgenerator.

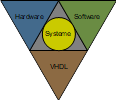

Die Steuerplatine für die Zentrale wird von einem Concerto-Prozessor verwaltet. Dieser besteht aus einem ARM-Core für die normale Kommunikation (Ethernet, USB, RS232) und einem C2000 Core für den Anschluss an die restliche Hardware über das Kommunikations-FPGA.

Restliche Hardware bedeutet die LWL-Interfaces zum Ring, Digital-IO, und Analog-IO über SPI ADCs/DACs. Die meisten Schnittstellen sind dabei potentialmäßig getrennt. Die Kommunikation zum FPGA wird über ein sogenanntes EPI-Interface, mit dem Datenströme in das FPGA geschrieben und von dort gelesen werden können.