Radarechosimulator für den automotive-Bereich

Die von mir zu enwickelnde Leiterplatte hat die Aufgabe, parametrierbare Radarechos in Echtzeit zu generieren und an eine IO-Platine weiterzuleiten. Des weiteren sind analoge und digitale Eingangssignale zu interpretieren und zu generieren. Drei weitere Schnittstellen (SPI, CAN und DSP-Link) wurden implementiert um die Radarechos zu parametrieren und den Simulator zu verwalten.

Die Eingangsstufe besteht aus einem DSP und einem Timing/Kommunikations-FPGA. Dieses FPGA ist mit SPI, CAN und analog/digital-IO verbunden (und natürlich auch mit dem DSP). Zusammen empfangen sie die Betriebsparameter und steuern die darauffolgende Signalverarbeitungsstufe.

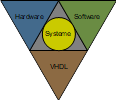

Die Signalverarbeitungsstufe des Simulators besteht aus vier identischen Modulen. Ein Modul besteht im wesentlichen aus einem FPGA und einem Signalprozessor. Dieses ist im VHDL-Teil weiter beschrieben.

Die Ergebnisse der Signalverarbeitungsstufe werden in der Ausgabestufe synchronisiert und an die Analogplatine weitergegeben. Dies geschieht durch ein FPGA welches die Signale zu Überwachungszwecken zusätzlich auch an das Timing-FPGA senden kann, wo sie dann über den DSP an die Anwendung weitergeleitet werden.

Signalverarbeitungsmodul

Für den zeitkritischen Kern des Algorithmus wurde ein spezielles Signalverarbeitungs-Modul entwickelt. Diese Realisierung wurde gewählt um den Simulator kostengünstig erweitern zu können.

Die Herausforderung bei der Entwicklung dieses Moduls lag in dem Finden einer geeigneten Struktur um den Algorithmus in Echtzeit umzusetzen und in der Programmierung des FPGAs.

Der Simulator wird in einer Closed-Loop betrieben und muss so die Echos in Echtzeit berechnen. Dadurch waren die Anforderungen an die Rechenleistung sehr hoch.

Realisiert wurde deswegen ein microcodierter Signalprozessor der Floatingpoint-Operationen u.a. auch Logarithmus ausführt und sich die Aufgabe mit einem handelsüblichen DSP teilt.

Darüberhinaus wurden in dem FPGA die Daten-Kommunikation, Kommandierung, Shared Memory und Bootlogik für den DSP integriert.