Digital-Down-Converter für eine PCI-Karte

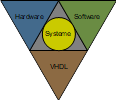

Für eine PCI-Karte wurde ein FPGA mit DDC realisiert.

Dieser führt im komplexen Basisband einen Frequenzzoom durch Mischer-Funktionen, CIC und FIR Tiefpassfilterungen mit Unterabtastungen durch. Die Aufgabe war zeitkritisch, da in einem ´breitbandigen Eingangssignal viele schmalbandige Kanäle überwacht werden sollten.

Des weiteren waren die Kommunikationsmechanismen mit der PCI-Bridge und dem externen Speicher so zu realisieren, dass die PC-Ressourcen möglichst wenig genutzt werden und der Speicher möglichst effizient genutzt werden.

Um die FPGA-Ressourcen weiter zu schonen wurde für die Signalverarbeitung ein synchrones Design mit 400/200/100 MHz gewählt. Der Teil des FPGAs der die Kommunikation mit dem PCI-Interface übernimmt, wurde mit 133/66 MHz durch FIFOs abgekoppelt, realisiert.